Difference between revisions of "GPU Firmware"

| Line 1: | Line 1: | ||

This page will document support for IO virtualization through various firmware functions. | GPUs have become highly complex systems containing a number of different embedded controllers. This page will attempt to document embedded GPU firmware and support for IO virtualization through various firmware functions. | ||

== Intel == | |||

=== Firmware Images === | |||

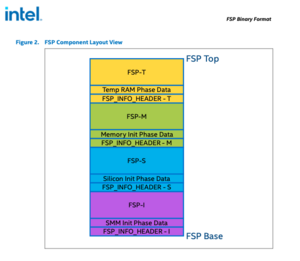

[[File:Screen Shot 2022-11-18 at 4.14.32 PM.png|alt=Figure 1: The FSP Binary Layout from Intel® Firmware Support Package External Architecture Specification.|thumb|Figure 1: The FSP Binary Layout from Intel® Firmware Support Package External Architecture Specification. [https://cdrdv2.intel.com/v1/dl/getContent/736809 Source]]] | |||

==== Intel Firmware Support Package (FSP) ==== | |||

Much like CPUs Intel's GPUs also contain the FSP. | |||

===== FSP Configuration ===== | |||

In the context of GPUs the FSP configures several functions of the device. | |||

Those functions are as follows: | |||

- GFSP Status | |||

- FIVR SSC Value | |||

- FIVR RFI Value | |||

- GT Subsystem Vendor ID | |||

- GT Subsystem Device ID | |||

- HDA Subsystem Vendor ID | |||

- HDA Subsystem Device ID | |||

- P2SB Enable | |||

- LMEBAR | |||

- GTMMADDR Prefetch Capability | |||

- [https://open-iov.org/index.php/Merged_Drivers Display Present] | |||

- I2C For Third Party Devices | |||

- I2C Device Address 1 | |||

- I2C Device Address 2 | |||

- I2C Bus Speed | |||

====== Editing FSP Configuration ====== | |||

The FSP configuration editor can be downloaded [https://github.com/tianocore/edk2/tree/master/IntelFsp2Pkg/Tools/ConfigEditor here] and it's user manual is available [https://github.com/tianocore/edk2/blob/master/IntelFsp2Pkg/Tools/UserManuals/ConfigEditorUserManual.md here]. | |||

===== FSP Binary Format ===== | |||

The FSP's binary layout is detailed within the [https://cdrdv2.intel.com/v1/dl/getContent/736809 Intel® FSP External Architecture Specification v2.4] on page 14. | |||

===== Known FSP Variations ===== | |||

=== Embedded Controllers === | |||

==== GuC ==== | |||

The Graphics micro (µ) Controller (GuC) is an embedded controller contained within Intel's Discrete Graphics (DG*) series GPUs. | |||

== Nvidia == | |||

=== Firmware Images === | |||

=== Embedded Controllers === | |||

==== Falcon ==== | |||

==== NvRISC ==== | |||

==== GSP ==== | |||

==== CMU ==== | |||

== AMD == | |||

Revision as of 21:16, 18 November 2022

GPUs have become highly complex systems containing a number of different embedded controllers. This page will attempt to document embedded GPU firmware and support for IO virtualization through various firmware functions.

Intel

Firmware Images

Intel Firmware Support Package (FSP)

Much like CPUs Intel's GPUs also contain the FSP.

FSP Configuration

In the context of GPUs the FSP configures several functions of the device.

Those functions are as follows:

- GFSP Status

- FIVR SSC Value

- FIVR RFI Value

- GT Subsystem Vendor ID

- GT Subsystem Device ID

- HDA Subsystem Vendor ID

- HDA Subsystem Device ID

- P2SB Enable

- LMEBAR

- GTMMADDR Prefetch Capability

- I2C For Third Party Devices

- I2C Device Address 1

- I2C Device Address 2

- I2C Bus Speed

Editing FSP Configuration

The FSP configuration editor can be downloaded here and it's user manual is available here.

FSP Binary Format

The FSP's binary layout is detailed within the Intel® FSP External Architecture Specification v2.4 on page 14.

Known FSP Variations

Embedded Controllers

GuC

The Graphics micro (µ) Controller (GuC) is an embedded controller contained within Intel's Discrete Graphics (DG*) series GPUs.